8-Bit Calculator

Overview

“To make an apple pie from scratch, you must first invent the universe” - Carl Sagan

With modern computers running impossibly long calculations in milliseconds, it’s easy to forget how much work is hiding behind something as simple as addition. I wanted to strip that abstraction away and build an 8-bit calculator from the ground up, using nothing but logic gates. No chips, no black boxes, no shortcuts. Just raw combinational logic, explicit state, and circuit switching that has to be correct for the system to function at all. The result is a fully gate-level calculator capable of selectable addition and subtraction, persistent memory, and deterministic behavior—essentially a small primitive ALU built by hand.

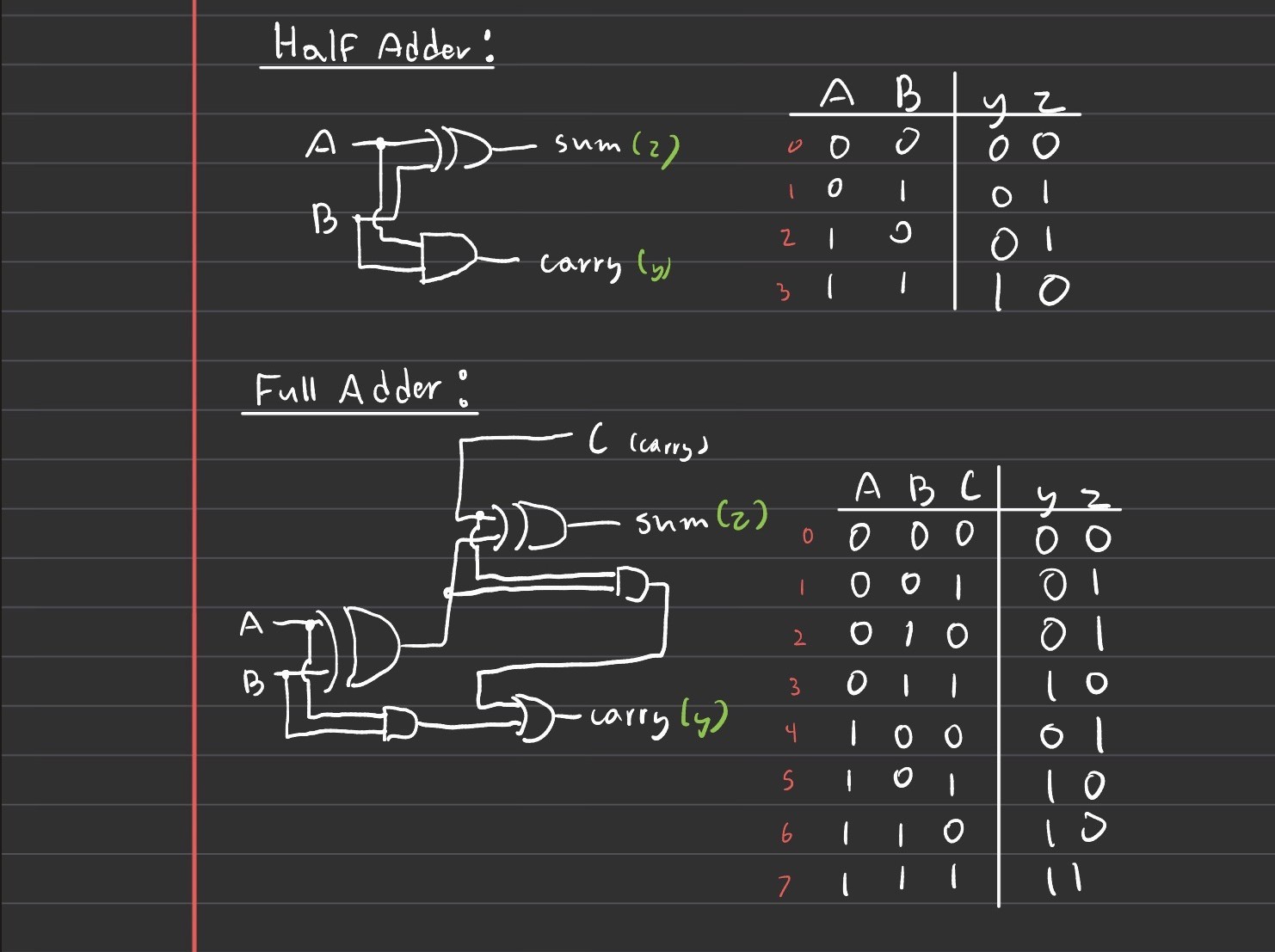

Arithmetic from First Principles

Imagine trying to bake a pie without an oven, how would you cook it? At the core of the design was the problem of arithmetic without abstraction. Addition and subtraction sound trivial until you’re responsible for every carry, borrow, and trace between any two gates.

8-bit ripple-carry adder and extended it to support subtraction by conditionally inverting operands and injecting carry-in, allowing both operations to share the same architecture.

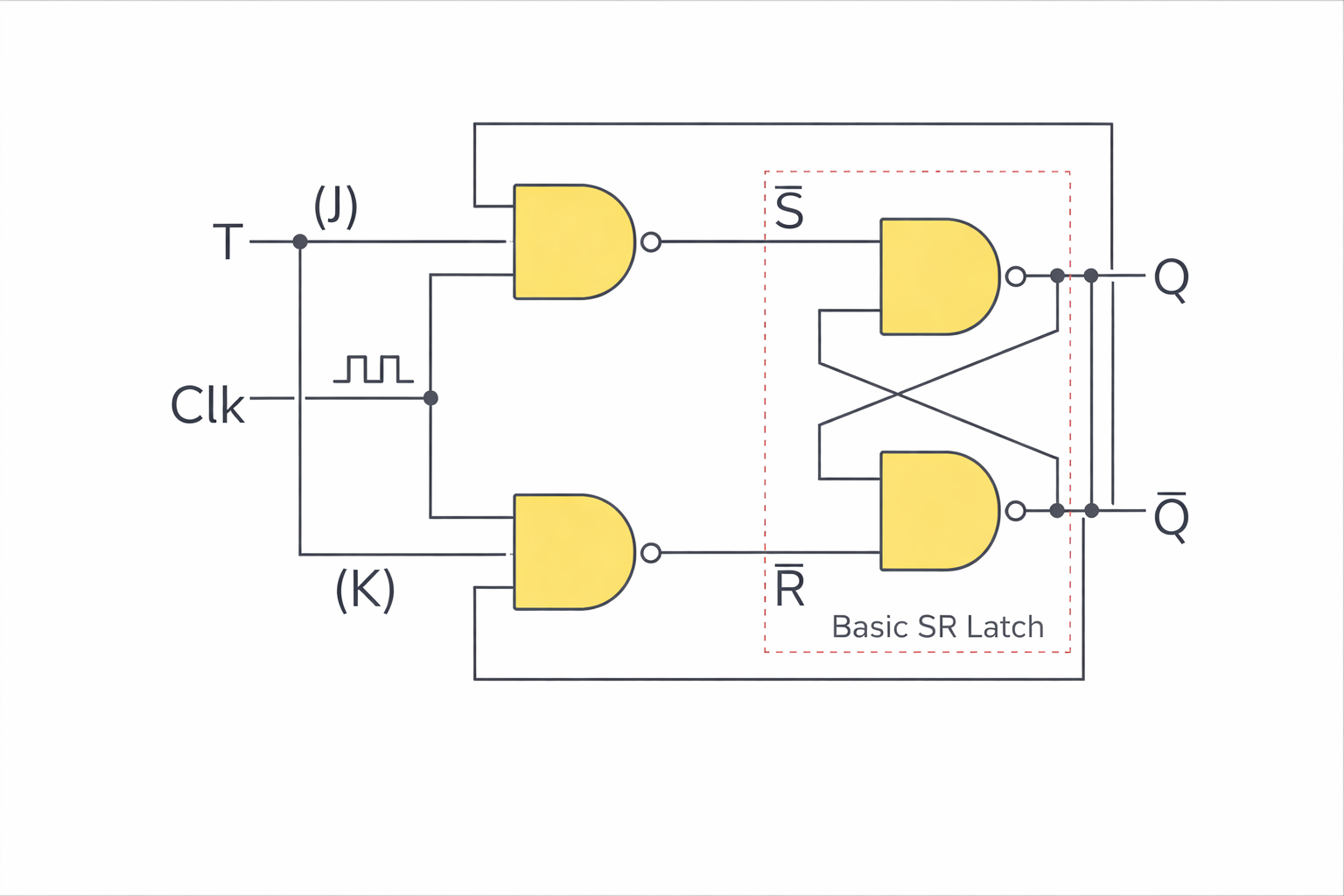

Memory

Having a pie is all but useless if you don’t have somewhere to store it so it can cool down. Arithmetic was only the first challenge of this project; storing results reliably without glitches, race conditions, or unintended updates was another issue.

I avoided JK flip‑flops because their J = K = 1 condition causes repeated bit flips, so instead I used T flip‑flops which guarantee stable, predictable state changes. From there, I built a clock‑gated memory system that allows values to persist indefinitely until the user explicitly overwrites them. This prevents repeated transitions during arithmetic operations, which would defeat the point of memory in the first place.

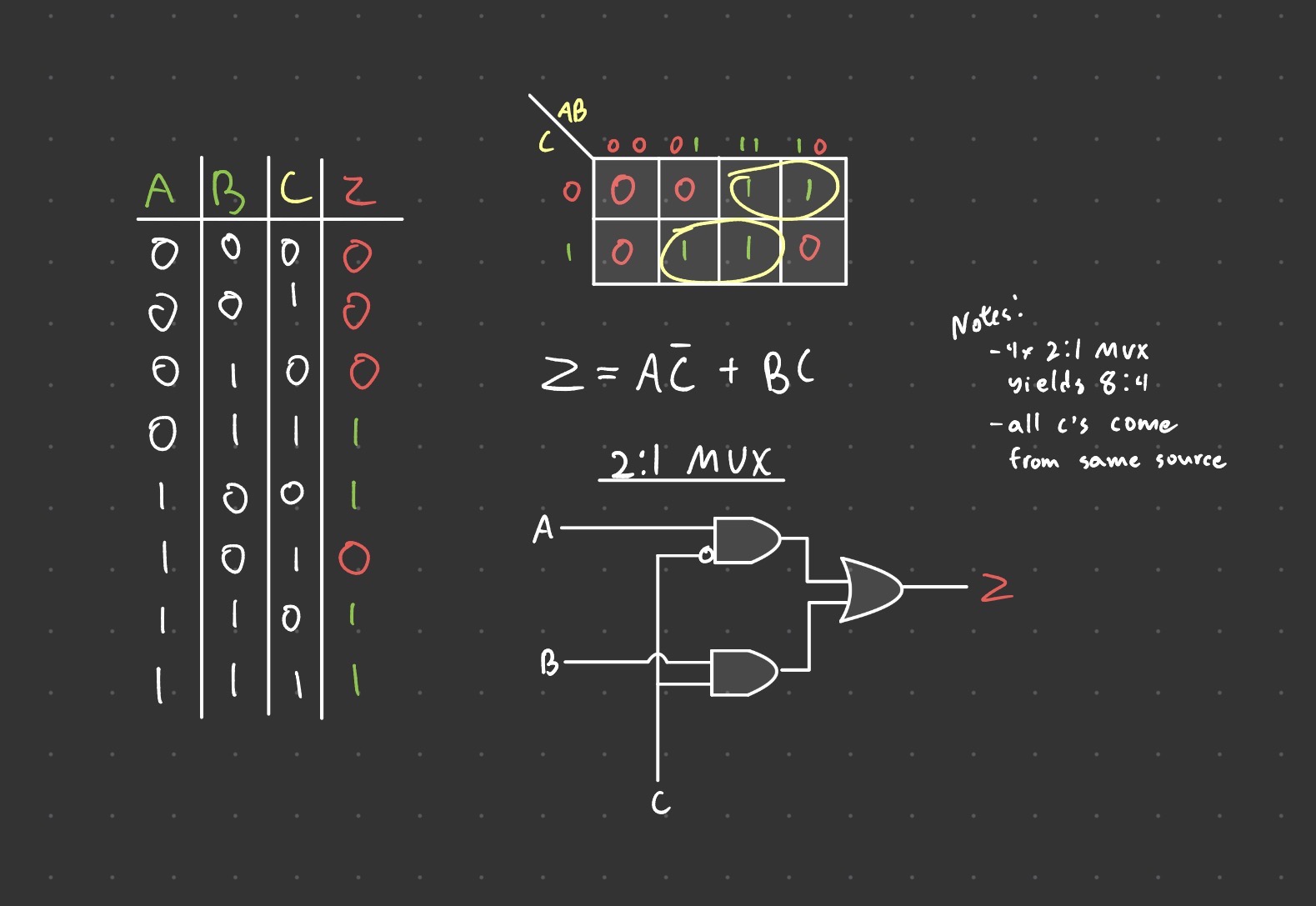

Selection

Selecting between live computation and stored state required its own solution, so I designed a custom 8:4 multiplexer using Karnaugh maps to minimize control logic and reduce gate depth. The reduced logic not only simplified routing but also improved timing robustness, ensuring clean state transitions even as multiple subsystems interact. The result is a calculator that behaves predictably because every state change is regulated.